## 6529 SINGLE PORT INTERFACE

#### **DESCRIPTION**

The 6529 is a static microprocessor compatible, 8-bit I/O Port with passive output pull-up devices. Data is written to the port when  $\overline{CS}$  and R/W are low. Data is read from the port when  $\overline{CS}$  is low and R/W is high. The passive output pull-ups allow a single bit to act as either an input or an output without I/O mode switching.

This device is provided with special circuitry to provide power-on reset. Under normal fast power-on conditions the outputs will initialize in the input high impedance state. With very slow or noisy power-up, there is some possibility the device will initialize with outputs driven low. It is recommended that the 6529 be interfaced to open collector output type devices.

#### TRUTH TABLE

| CS     | R/W         | D0-D7                                           |

|--------|-------------|-------------------------------------------------|

| L<br>L | L<br>H<br>X | Write to Output<br>Read from Input<br>Isolation |

L = LOW Level

H = HIGH Level X = Irrelevant

# ORDER INFORMATION MXS 6529

- FREQUENCY RANGE NO SUFFIX = 1 MHz A = 2 MHz B = 3 MHz

PACKAGE DESIGNATOR

C = Ceramic

P = Plastic

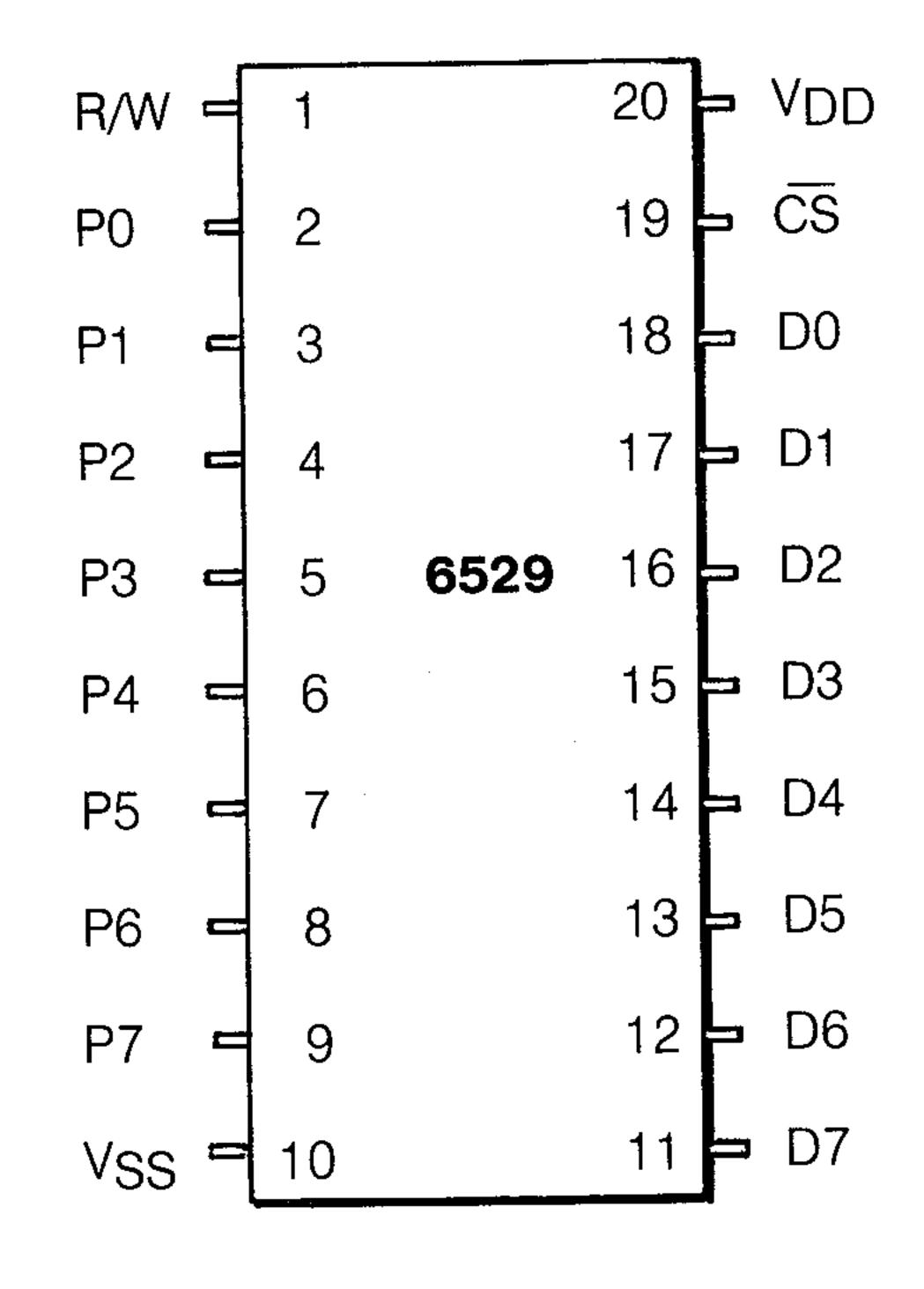

#### PIN CONFIGURATION

#### **MAXIMUM RATINGS**

| RATING                      | SYMBOL | VALUE          | UNIT |

|-----------------------------|--------|----------------|------|

| SUPPLY VOLTAGE              | VCC    | -0.3 to $+7.0$ | Vdc  |

| INPUT VOLTAGE               | Vin    | -0.3 to $+7.0$ | Vdc  |

| OPERATING TEMPERATURE RANGE | TA     | 0 to + 70      | °C   |

| STORAGE TEMPERATURE RANGE   | Tstg   | −55 to +150    | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this circuit.

CHARACTERISTICS ( $V_{CC} = 5.0V \pm 5\%$ ,  $V_{SS} = 0V$ ,  $T_A = 0^\circ$  to  $70^\circ$ C)

| CHARACTERISTIC                                                                                   | SYMBOL     | MIN          | MAX  | UNIT         |

|--------------------------------------------------------------------------------------------------|------------|--------------|------|--------------|

| Input High Voltage (Normal Operating Levels)                                                     | VIH        | +2.0         | VCC  | Vdc          |

| Input Low Voltage (Normal Operating Levels)                                                      | VIL        | -0.3         | +.8  | Vdc          |

| Input Leakage Current Vin = 0 to 5.0Vdc WRITE, CS                                                | IIN        |              | ±2.5 | μAdc         |

| Three-State (Off State Input Current) (Vin = 0.4 to 2.4 Vdc, VCC = Max) D0-D7                    | ITSI       |              | ±10  | JuAdc        |

| Output High Voltage<br>(VCC = Min, Load = -600µAdc, P0-P7)<br>(VCC = Min, Load = -200µAdc, D0D7) | VOH        | 2.4          |      | Vdc          |

| Output Low Voltage<br>(VCC = Max, Load = 6.4mAdc, P0-P7)<br>(VCC = Max, Load = 3.2mA, D0-D7)     | VOL        |              | +0.4 | Vdc          |

| Output High Current (Sourcing) P0-P7 (VOH = 2.4 Vdc) D0-D7                                       | IOH<br>IOH | -600<br>-200 |      | /uAdd        |

| Output Low Current (Sinking) P0-P7 (VOL = 0.4 Vdc) D0-D7                                         | IOL        | 6.4<br>3.2   |      | mAde<br>mAde |

| Supply Current                                                                                   | ICC        |              | 80   | mA           |

NOTE: Negative sign indicates outward current flow, positive indicates inward flow.

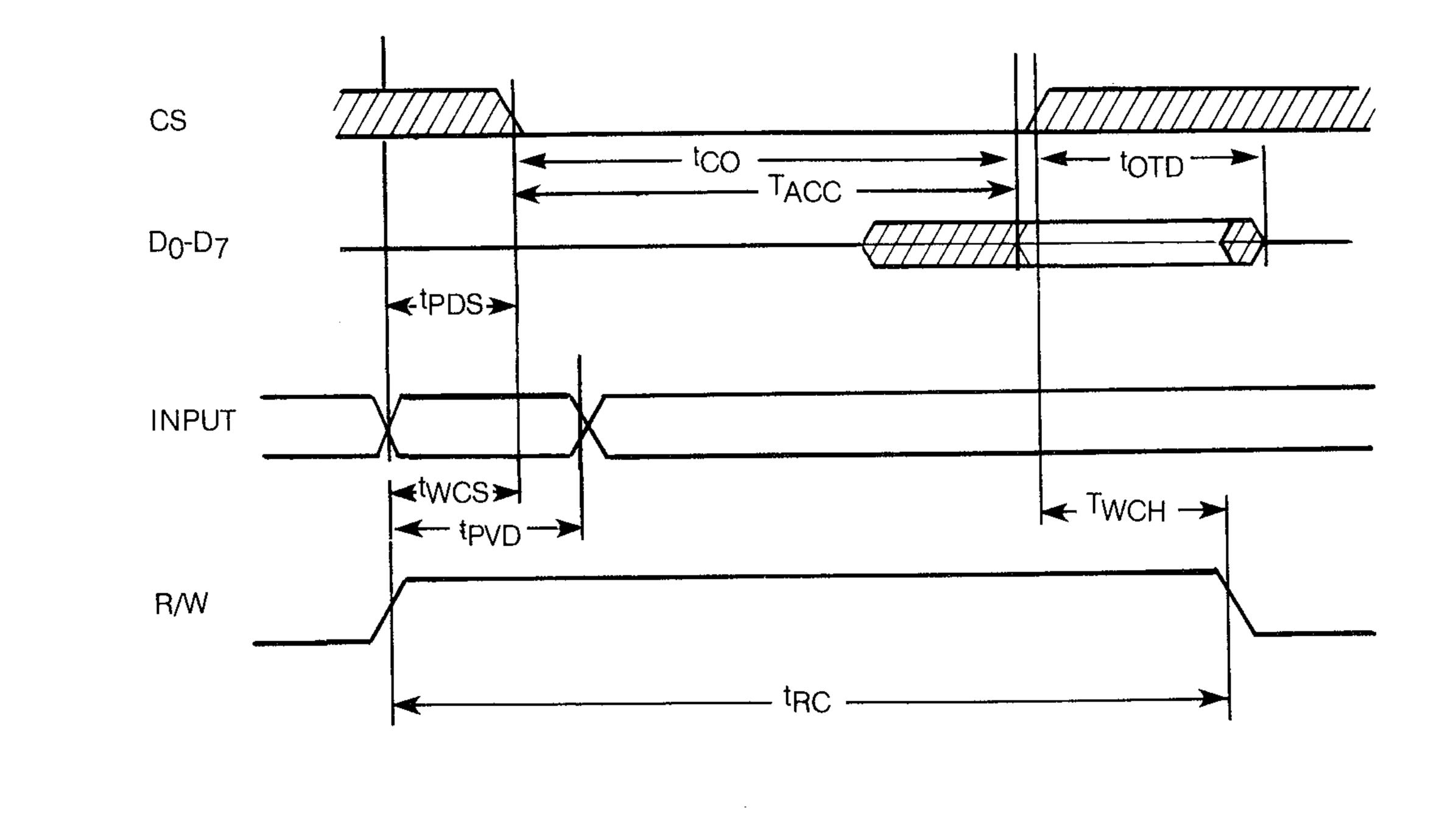

#### READ CYCLE TIMING DIAGRAM

### READ CYCLE CHARACTERISTICS

|        |                               | 1MHz |     | 2MHz |     | 3MHz |     |       |

|--------|-------------------------------|------|-----|------|-----|------|-----|-------|

| Symbol | Parameter                     | MIN  | MAX | MIN  | MAX | MIN  | MAX | UNITS |

| tACC   | Access time                   |      | 450 |      | 225 |      | 160 | nS    |

| tCO    | Chip Select to Output Valid   |      | 450 |      | 225 |      | 160 | nS    |

| tOTD   | Chip Deselected to Output Off | 20   | 120 | 20   | 120 | 20   | 120 | nS    |

| tPDS   | Peripheral Data Set-Up        | 120  |     | 60   |     | 40   |     | nS    |

| tPVD   | Peripheral Data Valid         | 150  |     | 150  |     | 150  |     | nS    |

| twcs   | Write to CS Setup             | 0    |     | 0    |     | 0    |     | nS    |

| twcr   | Write to CS Hold              | 0    |     | 0    |     | 0    |     | nS    |

|        |                               |      | ·   |      |     |      |     |       |

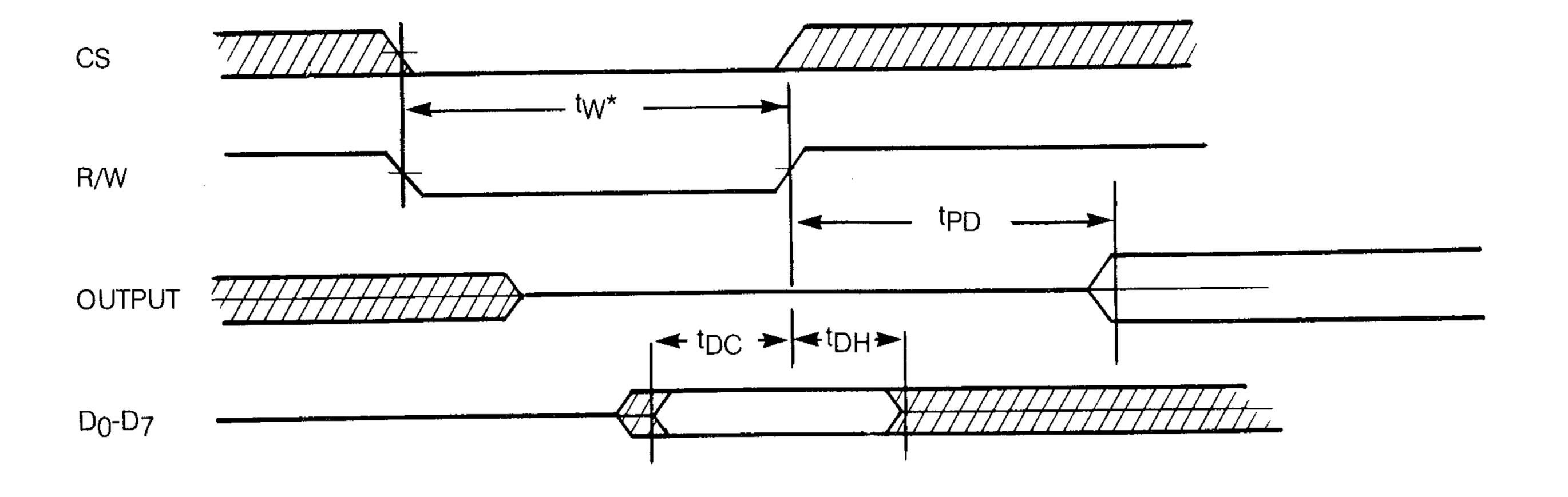

#### WRITE CYCLE TIMING DIAGRAM

#### WRITE CYCLE CHARACTERISTICS

|        |                            | 1MHz |      | 2MHz |     | 3MHz |     |       |

|--------|----------------------------|------|------|------|-----|------|-----|-------|

| Symbol | Parameter                  | MIN  | MAX  | MIN  | MAX | MIN  | MAX | UNITS |

| tw*    | Write Pulse Width          | 450  |      | 225  |     | 160  |     | nS    |

| tDC    | Data to CS Overlap         | 150  |      | 100  |     | 100  |     | nS    |

| tDH    | Data Hold                  | 0    |      | 0    |     | 0    |     | nS    |

| tPD    | Write to Peripheral Output |      | 1000 |      | 500 |      | 330 | nS    |

<sup>\*</sup>tw is measured from the latter of  $\overline{CS}$  or R/W going low to the earlier of  $\overline{CS}$  or R/W going high.

COMMODORE SEMICONDUCTOR GROUP reserves the right to make changes to any products herein to improve reliability, function or design. COMMODORE SEMICONDUCTOR GROUP does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.